# ELECTRONIC DEVICES FABRICATED AT CMOS BACKEND-COMPATIBLE TEMPERATURES

**Ihor Brunets**

The graduation committee consists of:

| chairman:        | prof. dr. ir. A. J. Mouthaan   | University of Twente     |

|------------------|--------------------------------|--------------------------|

| secretary:       | prof. dr. ir. A. J. Mouthaan   | University of Twente     |

| promoter:        | prof. dr. J. Schmitz           | University of Twente     |

| asst. promoter:  | dr. ir. J. Holleman            | University of Twente     |

| referent/expert: | dr. R. Ishihara                | Delft University of      |

|                  |                                | Technology / DIMES       |

| referent:        | dr. D. J. Gravesteijn          | NXP Research             |

| members:         | prof. dr. R. E. I. Schropp     | Utrecht University       |

|                  | prof. dr. ir. H. Hilgenkamp    | University of Twente     |

|                  | prof. dr. ir. R. A. M. Wolters | NXP Research             |

|                  |                                | and University of Twente |

The research was supported by Dutch Technology Foundation STW (project "Low temperature semiconductor device fabrication" TEL.6358) and carried out in the Semiconductor Components group, MESA+ Institute for Nanotechnology, University of Twente, The Netherlands.

Title: Electronic Devices fabricated at CMOS backend-compatible Temperatures

Author: Ihor Brunets (ihor@brunets.de)

ISBN: 978-90-365-2935-8

DOI: 10.399/1.9789036529358

Cover: illustration of the main process steps described in the dissertation: green-laser crystallization of preformed a-Si film and deposition of functional multilayer stack (SiO<sub>2</sub>, Si-nanodots, Al<sub>2</sub>O<sub>3</sub>, Al-metallization).

Cover design: Oleg Vorobyov

Copyright © 2009 by Ihor Brunets, Enschede, the Netherlands

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, in whole or in part without the prior written permission of the copyright owner.

iv

# ELECTRONIC DEVICES FABRICATED AT CMOS BACKEND-COMPATIBLE TEMPERATURES

## **PROEFSCHRIFT**

ter verkrijging van de graad van doctor

aan de Universiteit Twente

op gezag van de Rector Magnificus

prof. dr. H. Brinksma

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op donderdag 17 december 2009 om 13:15 uur

door

Ihor Brunets

geboren op 11 oktober 1977

de Lviv, Oekraïne

This dissertation is approved by:

prof. dr. J. Schmitz (promoter)

dr. J. Holleman (assistant promoter)

To my family.

# **Contents**

| 1 | Gen | eral introduction                                                          | 1  |

|---|-----|----------------------------------------------------------------------------|----|

|   | 1.1 | 3-D integration prolongs Moore's Law                                       | 2  |

|   | 1.2 | Aims of this work                                                          | 4  |

|   | 1.3 | Outline of the thesis                                                      | 5  |

| 2 | Exp | erimental                                                                  | 9  |

|   | 2.1 | Introduction                                                               | 10 |

|   | 2.2 | Design of the cluster reactor                                              | 10 |

|   | 2.3 | Laser crystallization equipment                                            | 12 |

|   | 2.4 | Spectroscopic ellipsometry                                                 | 14 |

|   | 2.5 | Photo- and electroluminescence measurement setup                           |    |

|   | 2.6 | Electrical measurements                                                    | 19 |

| 3 | For | nation of functional multilayer stacks                                     | 21 |

|   | 3.1 | Introduction                                                               | 22 |

|   | 3.2 | Memory cell multilayer structure                                           | 22 |

|   |     | 3.2.1 Formation of tunnelling oxide                                        | 22 |

|   |     | 3.2.2 Formation of Silicon Nanodots Layer                                  | 24 |

|   |     | 3.2.3 Atomic Layer Deposition of Alumina (Al <sub>2</sub> O <sub>3</sub> ) | 25 |

|   |     | 3.2.4 Atomic Layer Deposition of Titanium Nitride (TiN)                    | 26 |

|   |     | 3.2.5 Aluminium sputtering and patterning                                  | 27 |

|   | 3.3 | Light emitting multilayer structure                                        | 28 |

|   | 3.4 | Conclusions                                                                | 29 |

| 4 | Dep | osition of silicon nanodots (Si-ND)                                        | 31 |

|   | 4.1 | Introduction                                                               |    |

|   | 4.2 | Pre-deposition surface treatment                                           | 32 |

|   | 4.3  | Low Pressure Chemical Vapour Deposition of Si-ND            | 32 |

|---|------|-------------------------------------------------------------|----|

|   | 4.4  | Characterization of Si-ND                                   | 36 |

|   |      | 4.4.1 Spectroscopic Ellipsometry measurements               | 36 |

|   |      | 4.4.2 AFM characterization                                  | 39 |

|   |      | 4.4.3 TEM characterization                                  | 41 |

|   | 4.5  | Conclusions.                                                | 41 |

| 5 | Elec | tronic devices with embedded Si-ND                          | 43 |

|   | 5.1  | Introduction                                                | 44 |

|   | 5.2  | Non Volatile Memory (NVM)                                   | 45 |

|   |      | 5.2.1 Memory cell operation principle                       |    |

|   |      | 5.2.2 Tunnelling mechanisms                                 | 48 |

|   |      | 5.2.3 Memories with discrete floating gate                  | 50 |

|   | 5.3  | Memory cell characterization                                | 51 |

|   | 5.4  | Silicon nanodots for photonic application                   | 54 |

|   |      | 5.4.1 Photoluminescence and electroluminescence             |    |

|   | 5.5  | Conclusions                                                 | 58 |

| 6 | Lase | er crystallization of amorphous silicon                     | 59 |

|   | 6.1  | Introduction                                                |    |

|   | 6.2  | Green-Laser Crystallization                                 | 62 |

|   |      | 6.2.1 Crystallization of uniform silicon films              |    |

|   |      | 6.2.2 Grain boundary location control approach              |    |

|   |      | 6.2.3 Crystallization of preformed silicon films            | 67 |

|   |      | 6.2.4 Surface and texture analysis of crystallized films    | 69 |

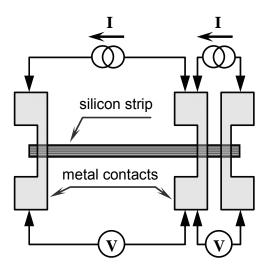

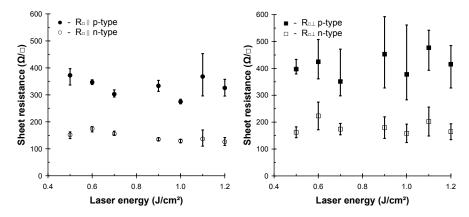

|   | 6.3  | Sheet resistance $(R_{\square})$ measurements               | 73 |

|   |      | 6.3.1 Fabrication of long diffusion area test-structures    | 73 |

|   |      | 6.3.2 Sheet resistance of laser crystallized films          | 74 |

|   | 6.4  | Surface and volume recombination in crystallized thin films | 76 |

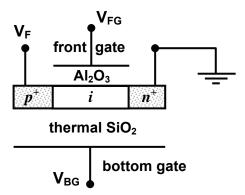

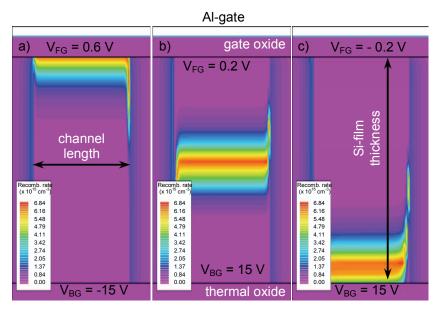

|   |      | 6.4.1 Modelled recombination in p-i-n diode                 | 76 |

|   |      | 6.4.2 Fabrication of p-i-n diodes                           | 78 |

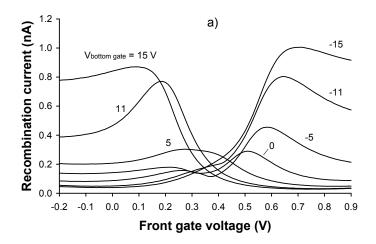

|   |      | 6.4.3 Measured recombination on p-i-n diode                 | 80 |

|   | 6.5  | TFTs with Al <sub>2</sub> O <sub>3</sub> gate oxide         | 82 |

|    |                         | 6.5.1 TFT fabrication                                                                                                                                                                                                                                                | 82  |  |

|----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

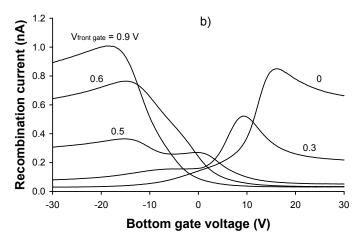

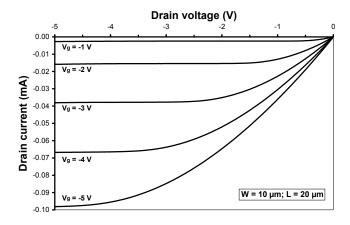

|    |                         | 6.5.2 TFT characterization                                                                                                                                                                                                                                           |     |  |

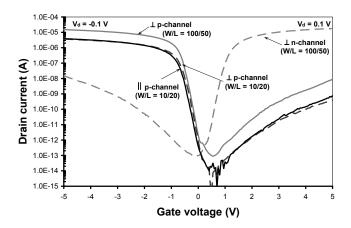

|    | 6.6                     | TFTs with SiO <sub>2</sub> gate oxide                                                                                                                                                                                                                                | 87  |  |

|    |                         | 6.6.1 TFT fabrication                                                                                                                                                                                                                                                | 87  |  |

|    |                         | 6.6.2 TFT characterization                                                                                                                                                                                                                                           | 89  |  |

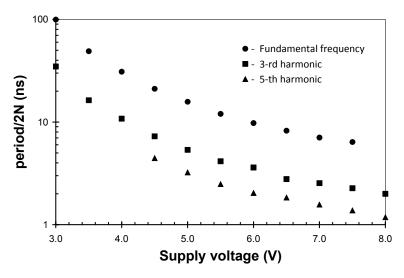

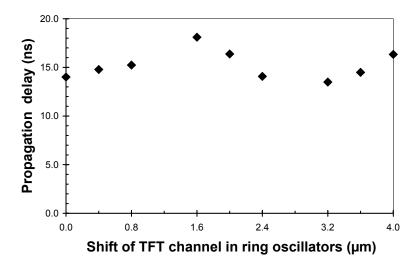

|    | 6.7                     | CMOS inverters and ring oscillators                                                                                                                                                                                                                                  | 93  |  |

|    | 6.8                     | Conclusion                                                                                                                                                                                                                                                           | 97  |  |

| 7  | Con                     | clusions and recommendations                                                                                                                                                                                                                                         | 99  |  |

|    | 7.1                     | Conclusions                                                                                                                                                                                                                                                          | 100 |  |

|    | 7.2                     | Recommendations                                                                                                                                                                                                                                                      | 101 |  |

| R  | eferei                  | nces                                                                                                                                                                                                                                                                 | 105 |  |

| Sı | ımma                    | 6.2 TFT characterization       89         MOS inverters and ring oscillators       93         onclusion       97         sions and recommendations       99         onclusions       100         ecommendations       101         s       105         ting       121 |     |  |

| Sa | men                     | vatting                                                                                                                                                                                                                                                              | 121 |  |

| Li | List of publications125 |                                                                                                                                                                                                                                                                      |     |  |

| A  | Acknowledgements        |                                                                                                                                                                                                                                                                      |     |  |

| Electronic Devices fabricated at CMOS backend-compatible Temperatures |  |

|-----------------------------------------------------------------------|--|

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

|                                                                       |  |

"No Exponential Is Forever:

But "Forever" Can Be Delayed!"

Gordon E. Moore (International Solid State Circuits Conference, Feb. 10, 2003)

# **General introduction**

# 1.1 3-D integration prolongs Moore's Law

The semiconductor industry experienced a tremendous technology development over the last half century. Until now it was possible to follow Moore's law [1] by scaling down the device dimensions and in the same time remaining a planar platform of integrated circuits (IC). It was achieved mainly by improvement of lithographic processes leading nowadays to nanometre-dimensions in complementary metal-oxide-semiconductor (CMOS) technology.

Although the industry is expected to follow the scaling road for at least another 10-15 years, further downscaling becomes much more challenging due to the several technical and commercial difficulties. The continuous dimensional scaling successively improved the transistor performance in terms of gate switching delay; however the global interconnect resistance-capacitance (RC) delay has gradually become the main circuit performance limiting factor. Additionally, the chip area enlargement necessary to facilitate the increased functionality leads to an enormous increase of the total interconnect length. As a result it will cause significant power dissipation problems deteriorating the performance of the ICs. Therefore, further functionality growth within conventional planar ICs would not be possible without compromising on performance, process complexity, or cost.

The perspective for using the third dimension not only for interconnects but also for introducing of the next active layers (i.e. device layers) was already envisaged by Feynman in his lecture "There's Plenty of Room at the Bottom," held at the annual meeting of the American Physical Society (California Institute of Technology, December 29, 1959) and published in 1960 [2]. So, three-dimensional (3-D) integration of ICs could be an effective solution to circumvent RC delay bottlenecks in today's interconnect-dominated chip performance.

An illustrative example of the semiconductor industry segment, which experiences a strong demand for development of a revolutionary fabrication process, is the memory market. Increase of bit capacity of the memory chips

Figure 1.1: Die Photograph of the Toshiba 56 nm 16 Gb NAND Flash (Source: Semiconductor Insights, 2007)

while keeping their compactness is achieved by following Moore's law also in memory cell design, similar to other IC technologies. However, flash memory downsizing is reaching its physical barriers earlier in comparison to downscaling in other integrated devices (e.g. problems with scaling of the blocking and especially tunnelling dielectrics, etc.). In the meantime, the size of the memory array increases in comparison to the size of the periphery due to aggressively increased bit capacity (see Figure 1.1). Therefore, memory chip development already now drives towards lower thermal budgets, and aims at 3-D integration [3-10].

There are a number of approaches available for a 3-D IC integration, so called post-singulation packaging or chip stacking (also known as chip-to-chip), and pre-singulation wafer-level integration (e.g. chip-to-wafer, wafer-to-wafer and full monolithic integration) [3, 7, 8, 10-16]. Each approach uses different alignment methods, bonding techniques etc., offering different vertical interconnect densities, and hence a various degree of improvement of ICs.

## 1.2 Aims of this work

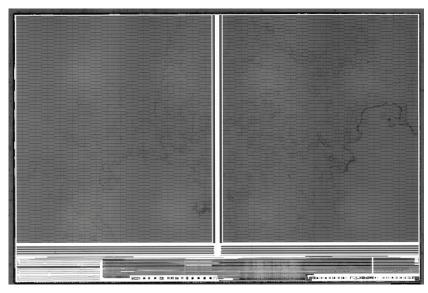

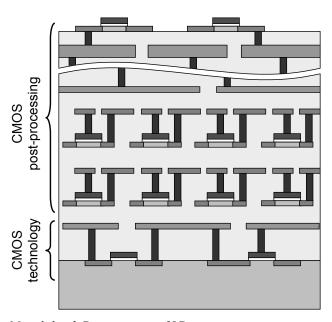

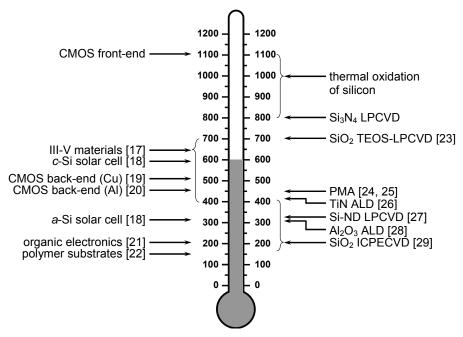

In this work we will focus on process steps required for the monolithic 3-D integration of ICs. In this approach, vertical integration of several active layers is done by their sequential processing starting from the bottommost device layer (shown in Figure 1.2). To avoid degradation of underlying devices, this approach demands tight thermal budgets during the formation of each next active layer and further device processing. Figure 1.3 gives a general overview of typical process temperatures for state-of-the-art technologies compared with several commonly used processing steps.

Therefore, the following technology key-points were investigated intensively:

- low-temperature deposition of semiconductor and dielectric films;

- grain boundary location controlled crystallization of the silicon films and dopant activation using a green laser.

Figure 1.2: Monolithic 3-D integration of IC.

Figure 1.3: Typical process temperatures for state-of-the-art technologies.

The performance advantages provided by the mentioned process steps are demonstrated using electronic devices realized at CMOS backend-compatible temperatures, i.e. temperatures well below 450 °C.

# 1.3 Outline of the thesis

# Chapter 2

Chapter 2 gives a general overview of the equipment used in this work for fabrication and analysis of the realized structures. The design of a cluster system and the development of deposition modes available to form low temperature semiconductor and dielectric layers are described. Then, the laser equipment used for crystallization and dopant activation in silicon films is shown. The description of measurement and analysis techniques employed in this work finalize the chapter.

# **Chapter 3**

An important issue during device processing is the formation of semiconducting and dielectric layers. The techniques used in this work, such as oxidation, various types of chemical vapour deposition, atomic layer deposition, are described in chapter 3. The processing of the multilayer structures for memories and photonic applications is reported.

# Chapter 4

This chapter deals with deposition and characterization of silicon nanodots - the key element of the realized memory cells and light emitting devices. The influence of the precursor gases, reactor conditions and substrate material on the silicon nucleation and film growth mechanisms are discussed in detail. Layers with high surface density of nanodots required for good memory performance are reported.

# Chapter 5

Chapter 5 presents the devices with embedded silicon nanodots realized at low processing temperatures. Advantages of the discontinuous floating gate for 3-D integrated memories are discussed. The performance of the memory cells with a layer of silicon nanodots as a floating gate is investigated. Optical characterisation of the functional multilayer stack with silicon nanodots embedded in an alumina matrix completes this chapter.

# Chapter 6

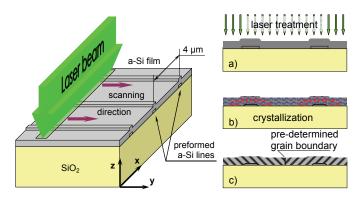

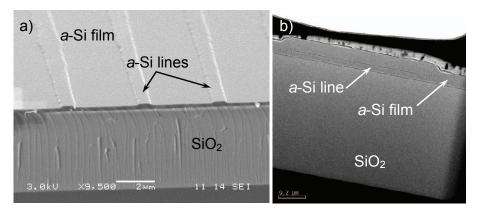

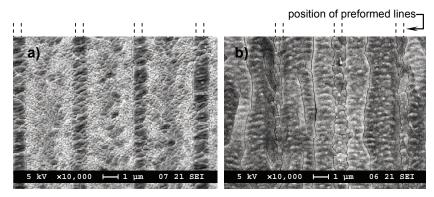

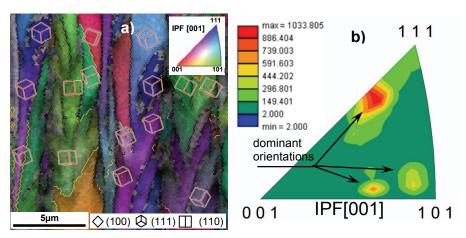

In this chapter a novel approach to make high-performance CMOS at low temperatures is presented. It starts with a brief overview of TFT technology development followed by a short description of silicon laser crystallization methods. The demand on grain boundary control in crystallized films is explained. It is proposed to use a pre-formed amorphous silicon film, which allows to predict the locations of the random grain boundaries after crystallization. Due to the simplicity of this method (i.e. it uses only available processing steps) it could be easily implemented in 3-D

integration. Numerous results of green-laser annealing employed for crystallization and dopant activation are presented. Sheet resistance measurements of anisotropic silicon films are interpreted and the dopant activation level is estimated. The recombination processes in crystallized films are modelled and the experimental data analysed. Fully functional electronic devices (i.e. TFTs, CMOS inverters and ring oscillators) manufactured at back-end compatible substrate temperatures on crystallized silicon films are demonstrated. They are extensively characterized and the results are discussed.

"Per varios usus artem experientia fecit"

"Through different exercises practice has brought skill"

Marcus Manilius

# 2

# **Experimental**

# 2.1 Introduction

This chapter contains a general overview of various specific equipment used in this work. First, the design and capability of the cluster deposition system are described. Then, the laser system used for silicon film crystallization and dopant annealing is presented. The second part of the chapter gives a short description of the measurement and analysis techniques used (i.e., spectroscopic ellipsometer, equipment for the electrical measurements, photo- and electroluminescence set-up).

# 2.2 Design of the cluster reactor

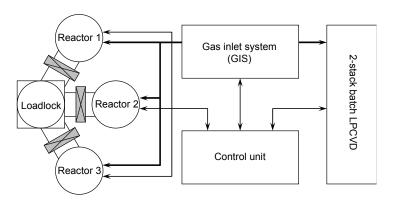

The deposition of the gate dielectrics (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>), silicon nanodot layers and passivation/metallization layers (TiN) was done in a cluster system consisting of three single-wafer reactors connected via a shared loadlock, shown in Figure 2.1. This design allows us to combine different techniques for the sequential deposition of various layers without vacuum break, preventing the undesirable reaction of deposited films with air. Reactor 1 is used for inductively coupled remote plasma enhanced chemical vapour deposition (ICPECVD) and is aimed at deposition nanocrystalline-Si and a-Si layers, as well as dielectric films. This reactor can also operate in an atomic layer deposition (ALD) or ICP-ALD mode. Reactors 2 and 3 operate either in a chemical vapour deposition (CVD) or ALD mode. Reactor 2 is used for the deposition of silicon, metal layers, and metal nitrides. Reactor 3 is mainly used as an ALD reactor for Al<sub>2</sub>O<sub>3</sub>.

The deposited layer thicknesses were determined with a Woollam M2000U spectroscopic ellipsometer described in section 2.4. The SE could be used in an "ex-situ" and "in-situ" (only in reactor 1) mode as well as in a "close-coupled" mode. Close-coupled means that deposition takes place in reactor 2 or 3 and that thickness is measured by transferring the wafer to reactor 1 without vacuum break.

Figure 2.1: Cluster system.

Reactor 1: ICPECVD for low-temperature deposition.

Reactor 2: deposition of metals and silicon in ALD and CVD modes.

*Reactor 3: deposition of Al*<sub>2</sub> $O_3$ .

The cluster system further includes two experimental LPCVD batch reactors, as shown in Figure 2.2. The loadlock, three single-wafer reactors and the two LPCVD batch reactors are PC-controlled, using a Labview application. This application provides the control of all pneumatic gas valves, the throttle valves, the valves for sample transport, the turbo pump controllers, the temperature controllers. The read-out data of the pressure, temperature and gas-flow sensors is displayed on the interface. Pneumatic gas valves are used in a common gas system to provide the five reactors with a choice of 20 semiconductor technology gases. Additionally, these pneumatic valves are used to pulse the reactive gases for the ALD process.

Figure 2.2: Schematic drawing of the cluster system.

# 2.3 Laser crystallization equipment

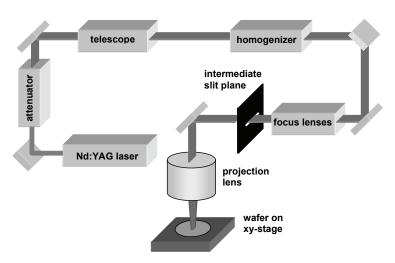

The silicon films were crystallized using the laser optical system LAVA available at INNOVAVENT GmbH, utilizing a green (515 or 532 nm) laser beam up to 54 mm length. A schematic block diagram of the optical system is shown in Figure 2.3.

The laser beam has a uniform top-hat profile along the x-direction and a

Figure 2.3: Block diagram of the laser optical system.

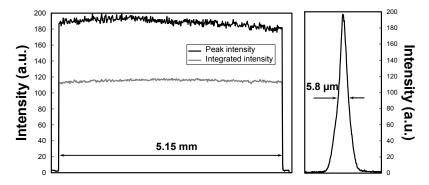

Gaussian profile along the (scanning) *y*-direction (see Figure 2.4). The beam intensity profile was measured at the wafer plane using a CCD camera and a 40× microscope. The average energy density in the beam was adjusted by an optical attenuator. The energy density was defined as the total pulse energy divided by the Full-Width Half-Maximum (FWHM) area of the beam [30-32].

For the film crystallization, we used the second harmonic of a diodepumped Yb:YAG thin disk laser (model JenLas® ASAMA) irradiating at a repetition rate of 50 kHz. The pulse duration was 206 ns. The applied beam length was 8 mm and the width was 5.8 µm, both FWHM values. The scan velocity was varied between 1 and 6 mm/s providing a beam overlap of 90 - 98 %. To define and shape the line edges, an adjustable mechanical slit embedded in the intermediate slit plate was used. It was imaged on the wafer surface with a 10× demagnification. Silicon film crystallization was investigated at laser energy densities ranging from 0.6 J/cm² to 1.2 J/cm².

The dopant activation was done by a laser optical system similar to that used for the crystallization. The applied laser energy density was  $0.4 \text{ J/cm}^2$ ; the beam length was 5.16 mm and the width was  $28.4 \text{ \mum}$ . The pulse duration was 300 ns with a repetition rate of 10.2 kHz, and the scan velocity

Figure 2.4: Laser beam intensity profiles: (a) along the x axis (perpendicular to the scanning direction) and (b) along the y axis (parallel to the scanning direction).

| Treatment                                 | Silicon crystallization | Dopant activation |

|-------------------------------------------|-------------------------|-------------------|

| Wavelength (nm)                           | 515                     | 515               |

| Laser energy density (J/cm <sup>2</sup> ) | 0.6 - 1.2               | 0.4               |

| Beam length (mm)                          | 8                       | 5.16              |

| Beam width (µm)                           | 5.8                     | 28.4              |

| Pulse duration (ns)                       | 206                     | 300               |

| Repetition rate (kHz)                     | 50                      | 10.2              |

| Scan velocity (mm/s)                      | 1 - 6                   | 14.5              |

| Beam overlap (%)                          | 98                      | 95                |

Table 2.1: Laser system settings.

was 14.5 mm/s, providing a beam overlap of 95 %. Under these conditions the dopant becomes active without silicon re-melting.

The summarized settings applied during the silicon film crystallization and dopant activation are shown in Table 2.1.

During the laser treatment the wafer was located on a high accuracy motorized xy-stage. The projection lens was mounted on a high precision z-stage providing accurate focus adjustment. The depth of focus was  $\pm$  10  $\mu$ m. The adjustment was done by making single pulse imprints on a test wafer followed by optical microscope inspection. The wafer stage, laser shutter and optical attenuator were computer controlled, so that the treatment steps with different energy densities and pulse overlaps were done automatically, at different locations on the wafer.

# 2.4 Spectroscopic ellipsometry

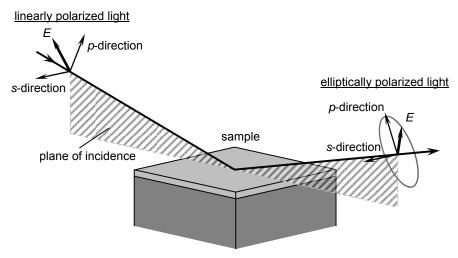

Ellipsometry is a very sensitive non-destructive surface and thin film optical measurement technique that uses polarized light and measures the polarisation state of the light beam reflected from the sample. Ellipsometry can be used to determine thin film thicknesses and thin film optical constants.

Figure 2.5: Interaction of polarized light with a sample during ellipsometric measurements.

During the ellipsometric measurements an input beam with known linear polarization state is launched onto the sample (as shown in Figure 2.5). The polarization state is described by specifying its components along two orthogonal axes, the so-called *p*- and *s*-directions, in the plane perpendicular to the direction of beam propagation. The *p*-direction is defined as lying in the plane of incidence (which is defined as the plane containing the incident and reflected beams and the vector normal to the sample surface). The s-direction (from Senkrecht, German for perpendicular) lies perpendicular to the *p*-direction. The *p*-direction, *s*-direction, and direction of propagation define a right-handed Cartesian coordinate system.

After reflection from the sample surface it is converted to an elliptically polarized beam. By measuring of the polarization state of the reflected beam values for ellipsometric parameters  $psi(\Psi)$  and  $delta(\Delta)$  are extracted.

The change in polarization state  $(\rho)$  is commonly expressed with  $\Psi$  and  $\Delta$  and defined in (2.1). These values are related to the ratio of Fresnel reflection coefficients  $\tilde{R}_p$  and  $\tilde{R}_s$  for p- and s-polarized light, respectively [33].

Figure 2.6: Spectroscopic ellipsometer Woollam M2000U in "ex-situ" measurement mode.

$$\rho = \tan(\Psi)e^{i\Delta} = \frac{\tilde{R}_p}{\tilde{R}_s}$$

(2.1)

In other words,  $tan(\Psi)$  is the magnitude of the reflectivity ratio, and  $\Delta$  is the phase.

In Spectroscopic Ellipsometry (SE), *psi* and *delta* values are measured as a function of wavelength. This yields much more information about the

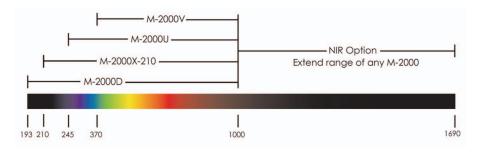

Figure 2.7: Spectral range of various spectroscopic ellipsometer systems.

sample. Therefore, it is possible to analyse the data in specific spectral regions where the required model parameters are more sensitive.

In this work the thickness of the deposited layers was determined by a Woollam M2000U spectroscopic ellipsometer with NIR (near-infrared) option (shown in Figure 2.6). The high-speed CCD detector collects over 700 wavelengths simultaneously, covering the spectral range of 245–1700 nm (Figure 2.7). The M-2000U could be used in "ex-situ" mode as shown in Figure 2.6. Additionally, the ellipsometer could be mounted on the process chamber to perform "in-situ" thin film monitoring and process control during LPCVD, PECVD, MOCVD, ALD, sputtering, E-beam evaporation, plasma etch, etc.

Thin film parameters such as thickness, optical constants, roughness, composition, etc., were extracted from the measured SE data using CompleteEASE software supplied by J. A. Woollam Co., Inc., which makes use of optical models and tabulated parameters.

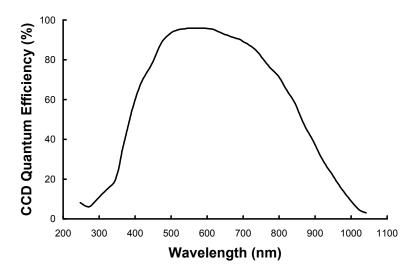

# 2.5 Photo- and electroluminescence measurement setup

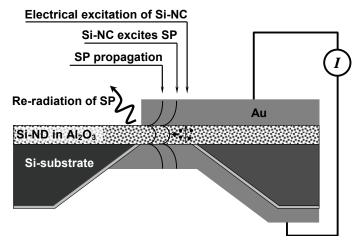

Photo- and electroluminescence measurements were performed on samples with silicon nanodots embedded in  $Al_2O_3$ , deposited at low-temperature using ALD (see Chapter 3). The optical measurements were done in the group of Prof. Dr. A. Polman at the FOM-Institute for Atomic and Molecular Physics. The 488 nm line of an argon-ion laser was used for excitation of the nanodots. The excitation power was typically  $1 \text{ W/cm}^2$ . The emitted light was collected with a f = 25 mm lens (NA = 0.45). Then the sample's emission spectrum was measured with a spectrograph Acton SP2300 equipped with a Si CCD-detector PIXIS:400B, both from Princeton Instruments. Quantum efficiency of the CCD detector is shown in Figure 2.8. A low-pass filter, placed in front of the spectrograph entrance slit was used to block the excitation wavelength [34].

Figure 2.8: Quantum efficiency of back-illuminated Si CCD-detector PIXIS:400B with permanent deep thermoelectric cooling.

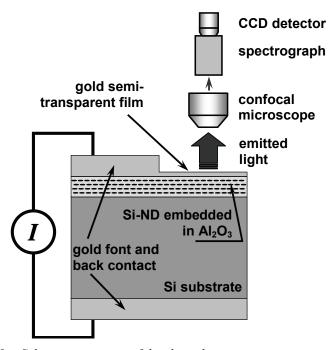

Figure 2.9: Schematic overview of the electroluminescence measurement set-up.

The electroluminescence was measured on the metal-insulator-silicon capacitor structures. A schematic cross-sectional set-up overview is shown in Figure 2.9. Samples with up to 4 layers of silicon nanodots embedded in alumina were investigated. To enable measuring the emitted light, a 20-nm thick semi-transparent layer of gold was additionally sputtered on the top surface (i.e. directly on the Al<sub>2</sub>O<sub>3</sub>/Si-NC layer stack). Then the electrically contacted sample was mounted under an inverted scanning confocal microscope. When biasing a sample the Si nanodots were excited by impact excitation [35] and the electroluminescence signal was measured.

# 2.6 Electrical measurements

Electrical measurements, including *C-V* and *I-V* characterisations, sheet resistance, static and dynamic characteristics of CMOS inverters were performed on a Karl Suss MicroTec PM300 Manual Probe Station equipped

Figure 2.10: Karl Suss MicroTec PM300 Manual Probe Station equipped with a Keithley 4200 SCS Semiconductor Characterization System.

with a Keithley 4200 SCS Semiconductor Characterization System including precision remote pre-amplifiers for ultrahigh resolution semiconductor measurements (shown in Figure 2.10). Keithley Interactive Test Environment (KITE) software interface was used to collect and analyse the measured data.

Dynamic characteristics of CMOS ring oscillators were measured using a Tektronix TDS 7404 Digital Phosphor Oscilloscope and HP 4145B Semiconductor Parameter Analyzer.

"Esse est percipi"

"To be is to be perceived"

George Berkeley

# 3

# Formation of functional multilayer stacks

### 3.1 Introduction

In this chapter a review of the deposition processes used in this work is given. The realised functional multilayer structures for application in floating memories and in light emitting devices are reported. Because a key element of these multilayer stacks, i.e. the layer of silicon nanodots (Si-ND), was investigated intensively, the discussion of Si-ND deposition and characterization is separately treated in Chapter 4.

# 3.2 Memory cell multilayer structure

Discrete silicon nanodots layer as a replacement for continuous floating gate in conventional non-volatile memories has been intensively studied already since 1996 [36]. Due to their high applicability in 3-D memory chip integration, nanodots deposition techniques gain a lot of attention in today's research [37, 38].

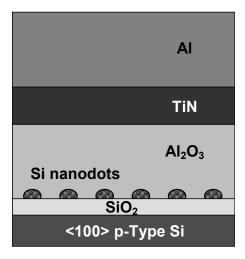

Realized in this work memory cell structures consist of a multilayer of Al/TiN/Al<sub>2</sub>O<sub>3</sub>/Si-ND/SiO<sub>2</sub>/Si. In this stack SiO<sub>2</sub> is the tunnelling dielectric and Al<sub>2</sub>O<sub>3</sub> the blocking dielectric. Due to the large difference in dielectric constant k, being 3.9 and 9 respectively for SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> the initial field across the SiO<sub>2</sub> is much larger thus creating a Fowler-Nordheim tunnelling through the SiO<sub>2</sub> where the Al<sub>2</sub>O<sub>3</sub> is still isolating. This Fowler-Nordheim breakdown however does not only depend on k but also on the electron barrier height between Si and dielectric. Since this value is almost equal for SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, k values dominate the tunnelling behaviour [39].

Because both thermal SiO<sub>2</sub> and ALD-Al<sub>2</sub>O<sub>3</sub>, as gate dielectrics are widely used and well-studied materials in integrated silicon devices [40-42], we choose them to be able to concentrate our research on other points, e.g. formation of silicon nanodots layer, etc.

# 3.2.1 Formation of tunnelling oxide

For memory cells two types of silicon oxide were utilized for tunnelling. 1) A conventional thermal oxide was used as a tunnelling dielectric in nonvolatile memories (described in Chapter 5) and 2) low temperature  $SiO_2$  deposited by means of ICPECVD used as a gate dielectric in TFTs on laser crystallized polysilicon stripes (described in Chapter 6). Before the formation of the oxide layer, a standard cleaning procedure was applied and the native oxide was etched in a solution of 0.3% HF and 0.3% HCl to avoid metal contaminations and to provide a hydrogen-terminated surface.

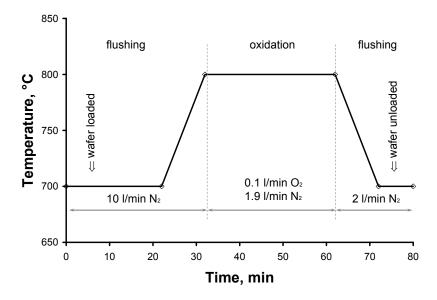

### Thermal oxide

To avoid formation of a low quality non-stoichiometric native oxide, a 2.6-nm thick thermal silicon dioxide layer was grown in a horizontal furnace by means of dry oxidation of the hydrogen-terminated <100> silicon wafer. The sample was loaded at 700°C in  $N_2$  and heated up to 800 °C in  $N_2$ , then oxidized at 800 °C in  $N_2/O_2$  (in a ratio of 19:1) and cooled down to 700 °C in  $N_2$  (shown in Figure 3.1). The oxide thickness was determined by the time that the wafer was exposed to the  $N_2/O_2$  ambient. Immediately after oxidation the wafer was transferred to the cluster reactor for further

Figure 3.1: Temperature profile used during dry oxidation.

deposition of the functional layers.

For the initial runs of memory stack we used thermal oxide as tunnelling oxide because the SiO<sub>2</sub>/Si system is very well known [41, 42] and it gave us the opportunity to investigate the other layers in the memory stack more independently. However, due to the high growth temperature, thermal oxide is not compatible with back-end process, where the temperatures can not exceed 450 °C. So, in a later stage of the research we switched to low temperature ICPECVD silicon oxide.

#### Low temperature ICPECVD silicon oxide

To maintain a low thermal budget during device fabrication, silicon dioxide gate dielectric layers were deposited in reactor 1 of the cluster system (see section 2.2) using remote inductively coupled plasma-enhanced chemical vapour deposition (ICPECVD) in an Ar-N<sub>2</sub>O-SiH<sub>4</sub> plasma at 150 °C and pressure 1 Pa. The gas phase contained 0.08% of SiH<sub>4</sub> and 18% of N<sub>2</sub>O - see [43] and [44] for more details. The thickness of the deposited oxides was determined "in-situ" by spectroscopic ellipsometer (see section 2.4).

#### 3.2.2 Formation of Silicon Nanodots Layer

After a standard cleaning and short dipping in a solution of 0.3% HF and 0.3% HCl, wafers with thermally grown SiO<sub>2</sub> were loaded into reactor 2 of the cluster system (see section 2.2). In case of the Si-ND deposition on low-temperature layers formed in the cluster system, the wafers were transferred to reactor 2 without any intermedium steps ensuring no vacuum break. Further, the deposition of the functional layer stack (TiN/Al<sub>2</sub>O<sub>3</sub>/Sinanodots) was done at temperatures ranging from 300 to 425 °C, without vacuum break. The layer with silicon nanodots was formed by LPCVD at 300-325 °C, using disilane (Si<sub>2</sub>H<sub>6</sub>) or trisilane (Si<sub>3</sub>H<sub>8</sub>, known as Silcore<sup>®</sup>) as the source gases. The deposition pressure ranged between 0.1 and 10 mbar. The deposition parameters, nucleation processes and silicon nanodots layer characterization are discussed in more detail in Chapter 4.

#### 3.2.3 Atomic Layer Deposition of Alumina (Al<sub>2</sub>O<sub>3</sub>)

Directly after the formation of Si-ND, the wafer was transferred to reactor 3 and covered with an 11-nm thick Al<sub>2</sub>O<sub>3</sub> layer (blocking oxide) grown by ALD in 126 cycles at a temperature of 300 °C.

Here it is assumed that the reader knows the basic principles of atomic layer deposition. A good documentation of these deposition techniques may be found in [45-49] and particularly results for ALD of Al<sub>2</sub>O<sub>3</sub> in used cluster system in [50].

In general the ALD process of metal oxides is based on sequential exposure of the sample's surface to the oxidizing and reduction precursor gases. In this way, the molecules of the reduction precursor first saturate the available bonding sites on the surface by chemisorption. Then the second precursor is used as an oxidizing agent. So, the ligands of the first precursor molecules are removed from the surface and new bonding states are created. If the gas-phase reaction between both precursors is avoided (e.g., by applying a purge step in-between) the sequential repetition of the described steps leads to the layer-by-layer growth of metal oxide. This provides a precise control over the thickness of the deposited layers, while the deposition rate remains constant (except the starting phase, when the surface has to be completely covered).

The ALD of  $Al_2O_3$  was based on the overall reaction (3.1) between  $Al(CH_3)_3$  (Trimethylaluminum, or TMA) and  $H_2O$ :

$$2 \text{ Al}(\text{CH}_3)_3 + 3 \text{H}_2\text{O} \rightarrow \text{Al}_2\text{O}_3 + 4 \text{CH}_4$$

(3.1)

To realize the ABAB... sequence of the self-saturating surface reactions (3.2) and (3.3), the wafer was consequently exposed to TMA and H<sub>2</sub>O, with a N<sub>2</sub>-purge cycle in between [28, 51]:

A:

$$[AlOH]_s + Al(CH_3)_3 \rightarrow [Al-O-Al(CH_3)_2]_s + CH_4$$

(3.2)

B:  $[Al-O-Al(CH_3)_2]_s + 2H_2O \rightarrow$

$\rightarrow [Al-O-Al(OH)_2]_s + 2CH_4$  (3.3)

were square brackets denote the surface (i.e. adsorbed) species.

The thickness of the deposited layer was measured with a spectroscopic ellipsometer after transferring the wafer to reactor 1 (as described in section 2.4).

#### 3.2.4 Atomic Layer Deposition of Titanium Nitride (TiN)

Due to the lower density of ALD-alumina in comparison to the bulk  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> [50] the weak diffusion of the oxidation species (e.g. water or oxygen) towards the encapsulated Si-ND during further processing steps is possible [52]. To prevent this unwanted diffusion into the blocking Al<sub>2</sub>O<sub>3</sub> layer, the wafer was transferred to reactor 2, where a 6-nm thick ALD layer of TiN was deposited in 150 ALD-cycles at 425 °C. The following overall reaction between TiCl<sub>4</sub> (Titaniumchloride) and NH<sub>3</sub> has been considered to take place:

$$6 \operatorname{TiCl}_4 + 8 \operatorname{NH}_3 \rightarrow 6 \operatorname{TiN} + 24 \operatorname{HCl} + \operatorname{N}_2 \tag{3.4}$$

where ammonia serves as a reducing agent and as a nitrogen source [26, 53-55].

To realize the *ABAB*... sequence of the self-saturating surface reactions, the wafer was consequently exposed to TiCl<sub>4</sub> (half-reaction A), followed by the N<sub>2</sub>-purge, and to NH<sub>3</sub> (half-reaction B), followed by the same purge. According to (3.4), both HCl and N<sub>2</sub> species are expected to be the volatile byproducts of ALD half-reaction too. However, exclusively HCl formation during deposition cycles was documented and no molecular nitrogen was detected [55]. Therefore, the ALD reaction scheme is better expressed by (3.5) and (3.6):

A:

$$\left[\text{Ti-NH}_{x}\right]_{s} + \text{TiCl}_{4} \rightarrow \left[\text{Ti-N-TiCl}_{4-x}\right]_{s} + x \text{HCl}$$

(3.5)

B:  $\left[\text{Ti-N-TiCl}_{4-x}\right]_{s} + \text{NH}_{3} \rightarrow \left[\text{Ti-N-Ti-NH}_{x-1}\right]_{s} + (4-x) \text{HCl}$  (3.6)

where square brackets denote the surface species.

Similarly to the ALD of Al<sub>2</sub>O<sub>3</sub> the thickness of the deposited layer was measured with the spectroscopic ellipsometer in reactor 1.

#### 3.2.5 Aluminium sputtering and patterning

Finally, the wafer was removed from the cluster system and both the front- and back-side metallization were realized by sputtering a 1-µm thick aluminium layer in the Oxford PL 400 sputtering system. The sputtering process may lead to significant surface heating [56, 57]. Therefore, to decrease the thermal impact on the multilayer structure the DC power supply was set at 700 W.

Circular MOS capacitors were finally realized by patterning the Al and TiN layers. First the aluminium layer is etched in aluminium-etchant at 55 °C. Then the wafer was rinsed with DI water followed by etching of the TiN at room temperature in approximately 1.5 minute. It was done in a mixture of ammonium hydroxide (NH<sub>4</sub>OH), hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>), and DI water (H<sub>2</sub>O) in a ratio of 1:1:5, also called Standard Clean solution (SC-1) or Ammonia and Hydrogen Peroxide Mixture (APM).

The post metallization furnace anneal was done in a  $H_2O/N_2$  ambient ( $N_2$  bubbling through DI water) for 10 minutes at 400 °C to provide interface dangling bonds passivation. A schematic cross-sectional overview of the realized structure is shown in Figure 3.2.

Figure 3.2: A schematic cross-section of the multilayer structure with encapsulated silicon nanodots.

#### 3.3 Light emitting multilayer structure

Light emitting functional multilayer stacks ( $Al_2O_3/Si-ND/...$ /Si-ND/Al $_2O_3$ ), consisting of multiple layers of silicon nanodots embedded in an alumina matrix were realized at low temperatures (300-325 °C) by a combination of ALD and CVD techniques.

Immediately after standard cleaning and native oxide etching in a solution of 0.3% HF and 0.3% HCl, the hydrogen-terminated p-type silicon wafers with <100> orientation were loaded into reactor 3 of the cluster

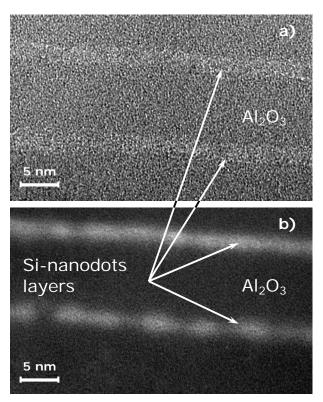

Figure 3.3: High Resolution (a) and Energy Filtered TEM images (b) depicting the cross-section of the multilayer stack with Si-ND embedded in an Al<sub>2</sub>O<sub>3</sub> matrix. In the EFTEM image the Si-containing areas appear bright, whereas oxides are dark. It is clearly visible from EFTEM that the Si-ND layers are discontinuous.

system (see section 2.2). There a 10- or 20-nm thick Al<sub>2</sub>O<sub>3</sub> layer was grown in respectively 120 or 245 ALD-cycles as described in section 3.2.3. Without vacuum beak, the wafer was transferred to reactor 2, where silicon nanodots were deposited in LPCVD mode from Si<sub>3</sub>H<sub>8</sub> at 325 °C and 1 mbar reactor pressure. The deposition time was 30 minutes resulting in 3.5 nm thick Sinanodots (details are discussed in Chapter 4). This sequence was repeated four times and completed with the last alumina layer.

The realized structures consist of four layers of nanodots embedded in five layers of alumina. Figure 3.3 shows a transmission electron microscope (TEM) image of a cross-section of a structure with 10 nm thick  $Al_2O_3$  layers. The energy filtered TEM analyses confirmed a discontinuous character of the silicon layers.

Finally, the wafer was removed from the cluster system and both the front- and back-side metallization were realized by sputtering gold layers (for the front-side metallization a 20 nm thick semi-transparent gold layer was used to provide enough light transmission and therefore to enable the electroluminescence measurements). A schematic cross-sectional overview of the realized structure is shown in Figure 2.8.

#### 3.4 Conclusions

Functional multilayer stacks with embedded Si-ND's were successfully designed and realized by CVD and ALD. The structures used for memory application were fabricated at temperatures below 425 °C except for the thermally grown silicon oxide layer. Optically active multilayer stacks consisting of silicon nanodots embedded in alumina were processed at temperatures below 325 °C. The investigated low temperature multilayer stacks (Al/TiN/Al<sub>2</sub>O<sub>3</sub>/Si-ND/SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/Si-ND/.. /Si-ND/Al<sub>2</sub>O<sub>3</sub>) have a potential to be used in 3-D integrated memories [37, 38, 58] and photonic devices [59, 60] (discussed in more detail in Chapter 5).

| Electronic Devices fabricated at CMOS backend-compatible Temperatur | Electronic | Devices | fabricated at | <b>CMOS</b> | backend-com | patible Tem | peratures |

|---------------------------------------------------------------------|------------|---------|---------------|-------------|-------------|-------------|-----------|

|---------------------------------------------------------------------|------------|---------|---------------|-------------|-------------|-------------|-----------|

"Est autem fides credere quod nondum vides; cuius fidei merces est videre quod credis"

"Faith is to believe what you do not see; the reward of this faith is to see what you believe"

St. Augustine

## Deposition of silicon nanodots (Si-ND)

#### 4.1 Introduction

The low-temperature deposition of silicon nanodots being the key element of memory cells and light emitting devices is discussed in this chapter. Formed nanodots layers are characterized using AFM, TEM techniques and spectroscopic ellipsometry. The influence of process parameters on the quality of the nanodot layers is shown.

#### 4.2 Pre-deposition surface treatment

The surface condition plays an important role especially during the starting phase of the deposition process. For the formation of Si nuclei, it is required that the Si precursor itself or intermediate gas phase products react easily with the surface. Reaction with the surface also requires reactive surface sites. To form the required dangling bonds, the dissociation energy of surface Si-O bonds is 4.8 eV while that of surface Si-O-H bonds is significantly lower (1.75 eV) [61]. Due to the large difference in bond energies, hydroxyl groups act as nucleation centres [62] resulting in a much higher nucleation rate of silicon (i.e. higher nanodot density) on a SiO<sub>2</sub> surface terminated by OH groups during the initial phase of LPCVD. In [61, 63] it has been demonstrated that Si nucleation takes place easier on dip etched SiO<sub>2</sub> surfaces, therefore to achieve the surface termination by OH groups and to avoid the metal contaminations, the wafers were briefly (around 1 minute) dipped in a solution of 0.3% HF and 0.3% HCl. Immediately after this dip, the wafers were placed into the loadlock of the cluster system.

### 4.3 Low Pressure Chemical Vapour Deposition of Si-ND

The layer with silicon nanodots was formed by LPCVD in reactor 2 at  $300\text{-}325\,^{\circ}\text{C}$ , using disilane ( $\text{Si}_2\text{H}_6$ ) or trisilane ( $\text{Si}_3\text{H}_8$ , known as Silcore <sup>®</sup>) as the source gases. The deposition pressure ranged between 0.1 and 10 mbar. The dramatic increase of silicon nucleation and growth rate, when using

Si<sub>3</sub>H<sub>8</sub> as a precursor, was reported for deposition temperatures between 410-500 °C [64] and higher. Therefore we expect to obtain a significantly higher Si-ND density using Si<sub>3</sub>H<sub>8</sub> instead of Si<sub>2</sub>H<sub>6</sub> also at lower temperatures.

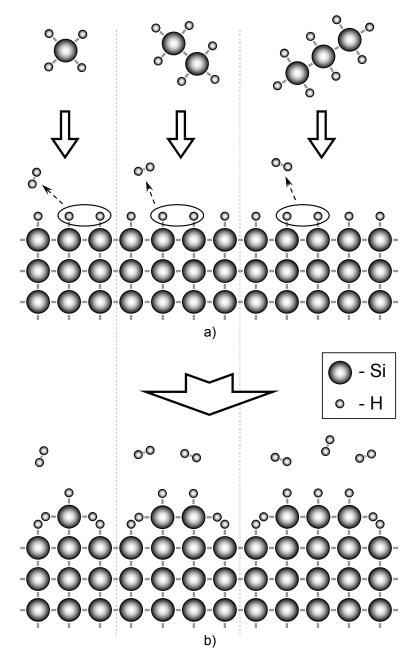

Regarding the CVD of silicon, there are three general surface reactions involving  $Si_2H_6$  (4.2),  $Si_3H_8$  (4.3) and  $SiH_4$  (4.1) precursors (schematically shown in Figure 4.1). One should bear in mind that silane can also appear due to gas-phase reactions [65].

$$\operatorname{SiH}_{4} + 2\left[\operatorname{Si}\right]_{s} \to 2\left[\operatorname{SiH}\right]_{s} + \left[\operatorname{Si}\right]_{h} + \operatorname{H}_{2} \tag{4.1}$$

$$Si_2H_6 + 2[Si]_s \rightarrow 2[SiH]_s + 2[Si]_b + 2H_2$$

(4.2)

$$Si_3H_8 + 2[Si]_s \rightarrow 2[SiH]_s + 3[Si]_h + 3H_2$$

(4.3)

where square brackets with subscription "s" denote surface species, whereas subscript "b" represents bulk silicon.

Although the reactivity increases in the order  $SiH_4$  -  $Si_2H_6$  -  $Si_3H_8$ , but the reaction probability is rather low for these species at low temperatures due to the very small fraction of the bare surface silicon atoms not covered with hydrogen. In other words, the reactive sticking coefficients of reactions (4.1), (4.2) and (4.3) are very small [66-68], since those direct adsorption mechanisms are defined by the activation energy of surface dehydrogenation ( $\approx 40 \text{ kcal/mol}$ ):

$$2[SiH]_s \rightarrow 2[Si]_s + H_2, \tag{4.4}$$

where  $[Si]_s$  is the free surface site needed for the surface reactions described above.  $[SiH]_s$  is the site occupied by H and therefore not reacting with  $SiH_4$ ,  $Si_2H_6$  and  $Si_3H_8$ . Only at elevated temperatures (higher than 700 °C) the direct adsorption becomes important [69].

At the same time, at sufficient gas pressures the following bimolecular gas-phase reactions sequences can occur [65] during CVD from disilane (4.5) and from silcore (4.6):

$$Si_{2}H_{6}+M^{2} \leftrightarrow SiH_{4}+SiH_{2}+M^{1} \leftrightarrow 2SiH_{2}+H_{2}+M^{0}$$

$$Si_{3}H_{8}+M^{3} \leftrightarrow Si_{2}H_{6}+SiH_{2}+M^{2} \leftrightarrow$$

$$\leftrightarrow SiH_{4}+2SiH_{2}+M^{1} \leftrightarrow 3SiH_{2}+H_{2}+M^{0},$$

$$(4.5)$$

Figure 4.1: General surface reactions during CVD of silicon from silane (Si $H_4$ ), disilane (Si $_2H_6$ ) and trisilane (Si $_3H_8$ ) mainly defined by the activation energy of surface dehydrogenation.

Figure 4.2: Bimolecular gas-phase reaction sequences during CVD of silicon from trisilane ( $Si_3H_8$ ) and subsequent surface insertion reactions of highly reactive silylene ( $SiH_2$ ).

where  $M^x$  (x = 0, 1, 2, 3) denotes any other gas molecule (as shown in Figure 4.2) and an energy of the molecule  $M^x$  is higher than of the molecule  $M^{x-1}$

As a result, highly reactive species such as  $SiH_2$  (silylene) with a reactive sticking coefficient close to unity are generated [65, 67, 68, 70]. Because of the gas-phase reactions, the rate of silylene formation strongly depends on the total pressure.

$$\operatorname{SiH}_{2} + \left[\operatorname{Si}\right]_{a} \to \left[\operatorname{Si}\right]_{b} + \left[\operatorname{Si}\right]_{c} + \operatorname{H}_{2} \tag{4.7}$$

This reactive specie can also insert on surface [SiH]<sub>s</sub> according to

$$\operatorname{SiH}_{2} + \left[\operatorname{SiH}\right]_{s} \to \left[\operatorname{Si}\right]_{b} + \left[\operatorname{SiH}_{3}\right]_{s} \to \left[\operatorname{Si}\right]_{b} + \left[\operatorname{SiH}\right]_{s} + \operatorname{H}_{2} \quad (4.8)$$

The use of trisilane, according to (4.6), ensures a higher concentration of silylene. Due to the very high reactivity of silylene, it is expected that a higher concentration of silylene will result in a higher nucleation rate providing a higher number of silicon nanodots even on a SiO<sub>2</sub> surface [27].

#### 4.4 Characterization of Si-ND

#### 4.4.1 Spectroscopic Ellipsometry measurements

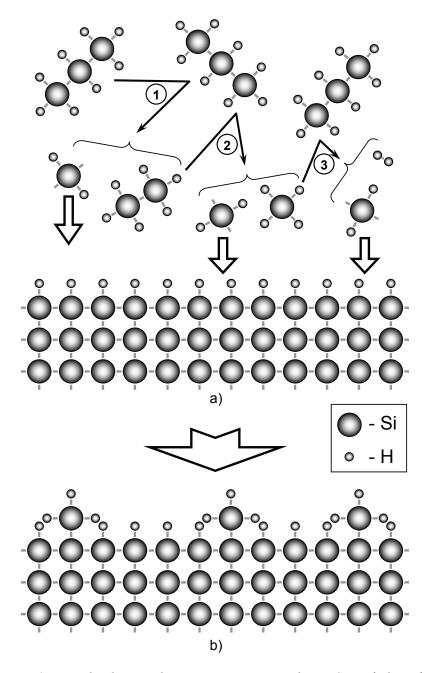

To investigate the starting phase of silicon nanodots formation during the deposition from trisilane (Si<sub>3</sub>H<sub>8</sub>) on SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> surfaces, a series of experiments with various deposition times was done. Two types of initial samples were used - with dip-etched thermally grown silicon oxide film and ALD Al<sub>2</sub>O<sub>3</sub> film, both 20 nm thick on silicon substrates. Directly after the silicon deposition the layer thickness was measured with the spectroscopic ellipsometer without vacuum break to avoid oxidation of the nanodots.

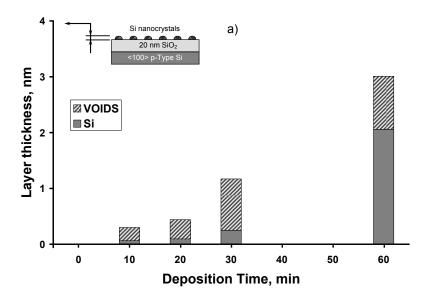

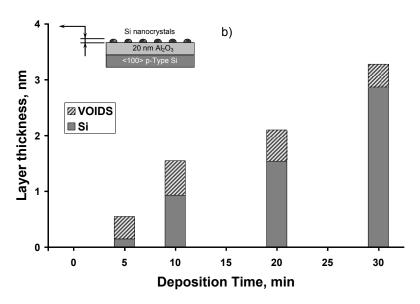

Besides thickness values also information about the continuity of the nanodot layer was extracted from the SE measurements by using a Maxwell-Garnett Effective Medium Approximation (EMA) of silicon and voids. The samples with Si-ND layers deposited at 1 mbar and 325 °C from trisilane were investigated. The results of deposition on both, silicon- and aluminium oxide surfaces are compared in Figure 4.3.

Figure 4.3: Layer thickness and composition extracted from SE measurements using a Maxwell-Garnett Effective Medium Approximation model for Silicon nanodot deposited on SiO<sub>2</sub> (a) and Al<sub>2</sub>O<sub>3</sub> (b) surfaces.

Deposition conditions: precursor gas flow – trisilane 5 ml/min; pressure - 1 mbar; temperature - 325 °C.

There is a clear difference in the nucleation phase at the beginning of the nanodots layer deposition. Because the LPCVD of nanodots on alumina surface is executed without vacuum break directly after the ALD of Al<sub>2</sub>O<sub>3</sub>, the surface is fully OH terminated. The hydroxyl groups acting as nucleation centres result in a very high surface density of generated silicon nuclei. Due to the high density of the nanodots layer even at the small nuclei sizes the spectroscopic ellipsometry equipment is sensitive enough to perform an immediate proper measurement (Figure 4.3b).

In contrast to this, when depositing on SiO<sub>2</sub> there is approximately a 20 minute delay before the spectroscopic ellipsometer can measure any significant changes in the nanodots layer (shown in Figure 4.3a). Deceitfully such a delay is called an "incubation time". However, this term is not completely correct, while the silicon nucleation starts immediately after the exposure of the surface to the precursor gas. Because of an insufficient resolution or sensitivity of the characterisation techniques it is not possible to obtain consistent measurement data from such a layer.

In our case, although the surface of SiO<sub>2</sub> was treated to be -OH terminated (see section 4.2), the number of hydroxyl groups on SiO<sub>2</sub> surface is lower in comparison to the alumina surface [71]. Additionally, the surface may change into Si-O termination during the pre-deposition steps after dipping (e.g., wafer loading, heating up, etc.). The lower surface density of the OH groups leads to the decreased density of generated silicon nucleus. The total volume of nucleated silicon remains negligible in comparison to the space between the dots (i.e., "voids"), therefore no information about Si-ND could be extracted from SE measurements until the ratio Si-ND/voids is below the threshold sensitivity of the equipment. Therefore, in [72] it is proposed to call the described delay as "apparent incubation time".

To achieve a higher density of Si-nanodots also on  $SiO_2$  surfaces a thin layer of ALD  $Al_2O_3$  (less than 1 nm, i.e., a few ALD cycles) can be formed before deposition of silicon. It acts as a functional surface for the further nucleation of silicon nanodots [73].

#### 4.4.2 AFM characterization

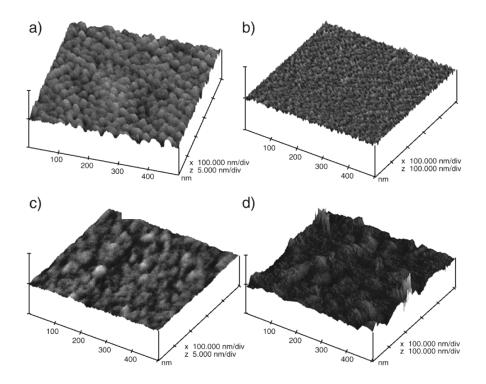

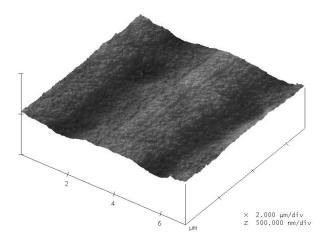

Atomic force microscopy was used to visualize the silicon nanodots after deposition. Samples with nanodots formed on SiO<sub>2</sub> layer were characterized without the covering Al<sub>2</sub>O<sub>3</sub> dielectric. We therefore expected the silicon nanodots to be oxidized immediately after exposing them to air (while transporting to the AFM system). Volume expansion during oxidation increases the dimensions of the nanodots, so that the physical size of the nanodots shown in Figure 4.4 is not representative of the encapsulated dots in our floating gate stacks.

Figure 4.4: The AFM image of oxidized Si-nanodot layers deposited at 325 °C from disilane at 10 mbar (a) and from trisilane at 1 mbar (b), 0.2 mbar (c), 10 mbar (d). To enable the observation of the nanodots, no upper protection layer was deposited. Deposition time 10 minutes.

The AFM surface images of a Si-nanodot layer deposited for 10 minutes at 10 mbar and 325 °C from disilane (Figure 4.4a), and at 1 mbar from trisilane (Figure 4.4b) and show a significantly increased concentration of the nanodots deposited from Silcore ( $\sim 1.9 \times 10^{12} \, \mathrm{cm}^{-2}$ ) in contrast to that deposited from disilane ( $\sim 0.2 \times 10^{12} \, \mathrm{cm}^{-2}$ ) compared in Table 4.1.

Using trisilane, a series of LPCVD experiments at 325 °C and different gas pressures was done. No deposition was observed at 0.2 mbar (see Figure 4.4c) and a very rough and non-uniform nanodot layer (Figure 4.4d) having  $R_a = 5.39$  nm was obtained at 10 mbar of deposition pressure.

For a successful industrial application of the described Si-ND deposition method a high reproducibility together with a high deposition speed is required. However, if the deposition process is very short (i.e. formation of nanodots within a minute), large run-to-run errors will be introduced by the equipment. At the same time, it should be much less than an hour, otherwise the stack growth takes impractically long. Therefore, for  $\mathrm{Si}_2\mathrm{H}_6$  the 10 mbar, and for  $\mathrm{Si}_3\mathrm{H}_8$  the 1 mbar could be considered as suitable process pressures during silicon nanodots formation at 325 °C. Due to the obtained higher nanodot density we can conclude that trisilane is a much better choice as a precursor gas for fabrication of Si-ND layers.

|                                                        | Precursor gas                  |      |                                |             |  |

|--------------------------------------------------------|--------------------------------|------|--------------------------------|-------------|--|

|                                                        | Si <sub>2</sub> H <sub>6</sub> |      | Si <sub>3</sub> H <sub>8</sub> |             |  |

| Pressure, mbar                                         | 10                             | 0.2  | 1.0                            | 10          |  |

| Thickness (SE), nm                                     | 1.98                           | 0    | 1.37                           | 16.87       |  |

| Si-nanodot density, ×10 <sup>12</sup> cm <sup>-2</sup> | $\sim 0.2$                     | 0    | ~ 1.9                          | $\sim 0.01$ |  |

| Composition Si/SiO <sub>2</sub>                        | 60/40                          | -    | 62/38                          | -           |  |

| rms, nm                                                | 0.25                           | 0.11 | 2.54                           | 7.10        |  |

| R <sub>a</sub> , nm                                    | 0.31                           | 0.08 | 1.97                           | 5.39        |  |

Table 4.1: Characteristics of deposited Si-nanodot layers. Deposition time 10 minutes (no upper protection layer was deposited) at 325 °C.

*Ex-situ* spectroscopic ellipsometer measurements of the nanodot layers (shown in Figure 4.4) provided us with the information about layer thickness and composition, as listed in Table 4.1.

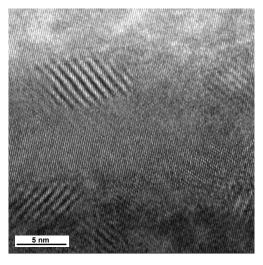

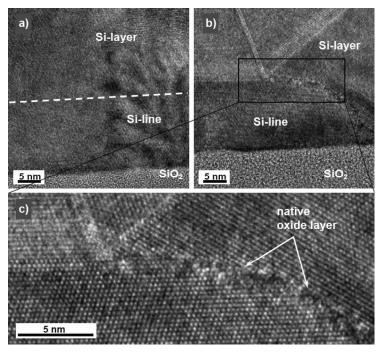

#### 4.4.3 TEM characterization

Figure 4.5 shows a high resolution top-view TEM image of the multilayer structure with encapsulated Si-nanodots deposited for 10 minutes from disilane at 325 °C and 10 mbar. The observed crystalline features are attributed to the nanodots. They appear to have a crystalline structure and to be oval in shape. The in-plane sizes of the nanodots are in the range of  $3 \div 8$  nm.

#### 4.5 Conclusions

The silicon nanodot layers suitable for application in memories and photonic devices were deposited using LPCVD at low temperatures, satisfying the thermal budget requirements for CMOS post-processing. The expected mechanisms of silicon nucleation and growth are discussed in

Figure 4.5: High-resolution TEM image displaying nanodots encapsulated into  $Al_2O_3$  dielectric layer

detail. The performed characterization of formed layers (e.g., AFM, TEM, SE) provide information about the obtained high nanodot surface density (up to  $1.9 \times 10^{12}$  cm<sup>-2</sup>). An increase in the growth rate and in the density of silicon nanodots deposited with Si<sub>3</sub>H<sub>8</sub> (Silcore<sup>®</sup>) as a precursor gas in comparison to Si<sub>2</sub>H<sub>6</sub> is demonstrated. Process parameters for obtaining a discrete high-density silicon nanodots layer are discussed. The importance of the substrate material and its surface termination is shown.

"Mater artium necessitas"

"Necessity is the mother of invention"

Πλάτων / Plato

## **Electronic devices with embedded Si-ND**

#### 5.1 Introduction

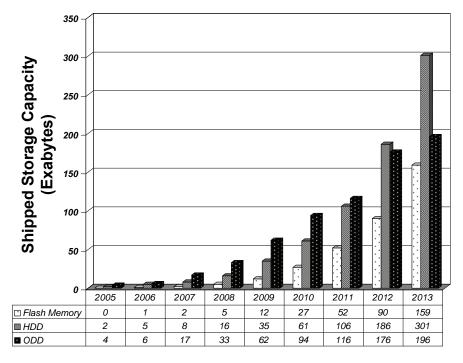

The constantly growing market of portable electronic devices (e.g., mobile phones, digital cameras, data storage devices, notebooks) demands low-cost, high-density, and highly reliable memories (such as SRAM, DRAM, EPROM, EEPROM and flash memories). A particular segment of the flash memories in this marked is rapidly increasing and is expected to approach the capacity volumes of the optical and hard disc drives in the near future (see Figure 5.1).

Comparing the dynamics of memory growth and memory scaling (discussed in section 1.1) one can conclude that there is a strong demand for new memory designs to fulfil today's market requirements. The vertical integration of cell arrays fabricated using processes with low thermal

Figure 5.1: Total consumer storage usage: optical disc drives (ODD), hard disk drives, and flash memories (Coughlin Associates, January 2008).

budgets, is one of the most promising solutions [4-8].

To overcome the challenges related to low processing temperatures, several new devices are presently investigated as replacements for the traditional floating gate stack; one of which being the nanocrystal memory cell [36-38, 74].

In this chapter an approach to realize silicon nanodot memory cells with a low thermal budget (below 400 °C) is shown. The use of a discontinuous floating gate enables the application of low temperature oxides in the functional multilayer stack, opening the way to 3-D memory structures inside the microchip's backend. The working principle of realized cells and their performance as memory device is discussed here.

Alternatively, photonic devices based on optically active silicon nanodots form another potential application area for Si-ND [59, 60]. Due to their CMOS-compatible processing the Si-ND embedded in an alumina matrix could be used as a light source for the external and internal optical data transfer in integrated circuits. The general optical characteristics of the proposed multilayer system are completing this chapter.

#### 5.2 Non Volatile Memory (NVM)

There is a number of memory types available for non volatile data storage in solid-state circuits such as read-only memory (ROM), programmable read-only memory (PROM), erasable and programmable read-only memory (EPROM), ultraviolet erasable (UVPROM) and electrically erasable (EEPROM). An important subcategory of EEPROM is a flash memory, where the entire memory array or large blocks of the memory array are electrically erased at once. This feature provides faster erase and programming times, smaller cell size and higher cell density (in comparison to EEPROM) leading to lower costs per bit.

The general non volatile memory concept based on modulation of the threshold voltage of the metal-oxide semiconductor field effect transistor (MOSFET) structure, was proposed by I.M. Ross already in 1957 [75]. The next important step was realized in 1967, when D. Kahng and S.M. Sze

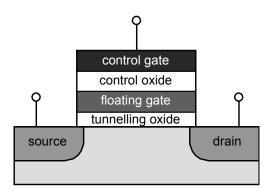

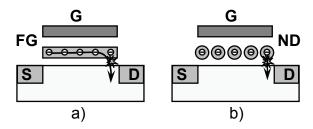

Figure 5.2: Schematic cross-section of the flash memory cell.

reported the first memory device with floating-gate structure [76]. There, an additionally introduced conducting charge trapping layer (floating gate) inside of the gate oxide layer (shown in Figure 5.2) enables a non-volatile information storage mechanism. In the same year, Wegener et al. suggested the use of a Si<sub>3</sub>N<sub>4</sub> dielectric with a high charge trap density as charge storage region in MNOS (Metal-Nitride-Oxide-Semiconductor) memory cells [77].

Since then, an intensive research on floating-gate non-volatile memories has been carried out to enhance their performance (i.e., high speed, high density and low power consumption) and to reduce the production costs. At the moment, flash memory is the fastest growing segment of the memory market and therefore receives enormous attention. In current flash memory technology, the gate dielectrics thicknesses (both tunnelling and blocking) are hardly scalable. As a consequence, the operating voltages of flash memories can not be reduced significantly below their current level.

These hindrances stimulate a continuous research on new cell designs and IC architecture. As will be shown further in this chapter, the replacement of the conventional floating gate with a layer of silicon nanodots together with implementation of the dielectric layers formed at low temperatures (see Chapter 3) enables the realization of the non-volatile memory cells with noticeably reduced thermal budget during the processing. This is opening an opportunity to integrate the memory cell arrays in the third dimension.

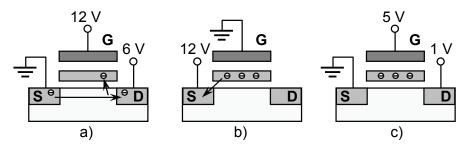

Figure 5.3: Example of flash memory with continuous floating gate (a) program, (b) erase and (c) read operations.

#### 5.2.1 Memory cell operation principle

The operational principle of the flash memory is based on the charge storage in the floating gate (functioning as a charge trapping layer) of a MOSFET (shown in Figure 5.3), inducing a modulation of the device threshold voltage. The programming or erasing steps are realized by applying appropriate voltages to the control gate, source, and drain, so that the charge carriers can tunnel through the tunnelling oxide toward or away from the floating gate (Figure 5.3a,b).

After programming, the charge stored in the floating gate causes a threshold voltage shift equal to [78]:

$$\Delta V_T = \frac{Q_T}{\varepsilon_i} d_i \tag{5.1}$$

where  $d_i$  is the thickness and  $\varepsilon_i$  is the dielectric constant of the blocking oxide (see Figure 5.2) and  $Q_T$  is the charge per unit area.

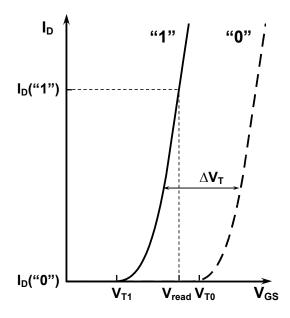

The read-out of a flash memory is done by applying the gate voltage  $V_{\text{read}}$  with a value between the two possible threshold voltages and measuring the drain current. As shown in Figure 5.4, in one state the transistor is conducting current (state "1"), while, in another, the transistor is in cut off (state "0"). If the power supply is interrupted, the stored charge will remain trapped in the floating gate providing a non-volatility of the memory cell.

Figure 5.4: I-V Curves of the non volatile memory cell in "1" erased state and "0" programmed state.

#### 5.2.2 Tunnelling mechanisms

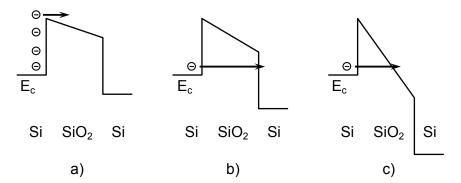

During the programming and erasing steps two different mechanisms can be used to transport the charge carriers through the tunnelling dielectric (i.e. across the potential barrier): hot electron injection and Fowler-Nordheim tunnelling [78].

At large applied drain biases, the induced large electric field in the channel of an NMOS transistor is used to provide electrons with sufficient energy (i.e. hot electrons) to get over the barrier into the conduction band of the dielectric (shown in Figure 5.5a). This mechanism is called "hot electron injection" and is widely used for programming of the memory cells. However, the required high drain and gate voltages result in very high currents and therefore make the programming process extremely power consuming. Another disadvantage of the shown tunnelling mechanism is that it can be applied only for programming and not for erasing of the cell.

When a low (read) voltage is applied to the gate of the MOS transistor the shape of the energy barrier across the tunnelling oxide is trapezoidal. It is possible for electrons to tunnel through such a barrier directly to the conduction band of the next electrode (shown in Figure 5.5b). However, to ensure good retention characteristics of the memory cell the leakage current across the tunnelling oxide ideally should be equal to zero. Therefore, due to the reliability concerns in memory devices this type of tunnelling has to be negligible to provide the low leakage currents.

In case of high (program/erase) gate voltages, high leakage currents across the tunnelling oxide are required. When the effective barrier has a triangular shape, being narrower than the thickness of the tunnelling oxide, Fowler-Nordheim tunnelling can occur. In this case, electrons tunnel to the conduction band of the dielectric (as shown in Figure 5.5c). In order to provide fast programming and erasing steps it is required to apply a high electric field (in the range of 10 MV/cm) to ensure the Fowler-Nordheim tunnelling through silicon oxide. The strong advantage of this tunnelling mechanism is its low power consumption. This makes it possible to simultaneously erase large memory array blocks – the main merit of the flash memory.

Figure 5.5: Energy diagram of the conduction band during hot electron injection (a), direct tunnelling (b) and Fowler-Nordheim tunnelling (c).

Figure 5.6: Possible leakage path in the tunnel oxide in a non-volatile memory cell with a continuous floating gate (a) and with nanodots (b). Once the continuous FG is shorted due to a defect in the tunnel oxide it can drain all stored (programmed) charge out from the FG. In a discontinuous FG the charge state is much less dependent on local leaks in the gate oxide which will discharge only a single nanodot isolated from others. That will reduce the impact of defects present in low-temperature dielectrics.

#### 5.2.3 Memories with discrete floating gate

In this work an approach to fabricate silicon-nanodot memory cells with a low thermal budget (below 425 °C) is investigated. In this perspective, the advantage of the discontinuous nanodot floating gate over continuous floating gates is that the charge state is much less dependent on local leaks in the gate oxide (see Figure 5.6). This allows the use of CVD gate oxides with a higher density of weak spots compared to thermally grown oxide.

The major benefits provided by the use of a discrete floating gate are the increase of the memory's retention time, an ability to scale the tunnelling oxide thickness, a minimized drain-to-floating-gate coupling and perspective to realize multi-bit storage devices [37]. Additionally, the possibility to fabricate memory cells on re-crystallized amorphous-silicon layers, keeping thereby the total thermal budget of the process low, opens the way to 3-D memory structures inside the microchip's backend.

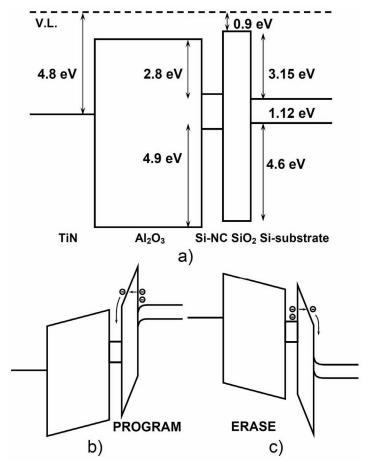

Figure 5.7: Energy band diagrams of multilayer structure with encapsulated Sinanocrystals under flatband condition (a), during programming (b) and erasing (c) cycles. Si-nanodots have an increased band gap compared to bulk Si [79].

#### 5.3 Memory cell characterization

In this work, the functional multilayer Al/TiN/Al<sub>2</sub>O<sub>3</sub>/Si-ND/SiO<sub>2</sub>/Si stack (shown in Figure 3.2) was realized according to the process flow described in subchapter 3.2. As already mentioned, two different materials were chosen for the tunnel and blocking gate dielectrics (i.e. silicon dioxide

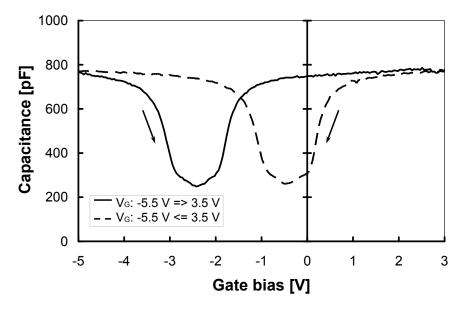

Figure 5.8: Quasi-static C-V hysteresis curves obtained during programming and erasing cycles for MOS structures with encapsulated silicon nanocrystals. Applied gate-substrate voltages:  $V_{G\,prog}=3.5\,V$  and  $V_{G\,erase}=-5.5\,V$ .

with k = 3.9 and alumina with k = 9, respectively), providing an energy band structure required for Fowler-Nordheim tunnelling through the tunnel oxide.

Figure 5.7a shows a schematic energy band diagram of the realized multilayer structure under flat band conditions according to [39, 80]. The encapsulated silicon nanocrystals are expected to act as charge trapping centres. During programming and erasing cycles due to the different dielectric material of tunnel and blocking oxides there is a much higher electric field induced across the thin SiO<sub>2</sub> film (see Figure 5.7b-c). That ensures the Fowler-Nordheim tunnelling mechanism to dominate during the charge carrier transport between the substrate and the nanocrystals, and at the same time prevents tunnelling through the blocking oxide.

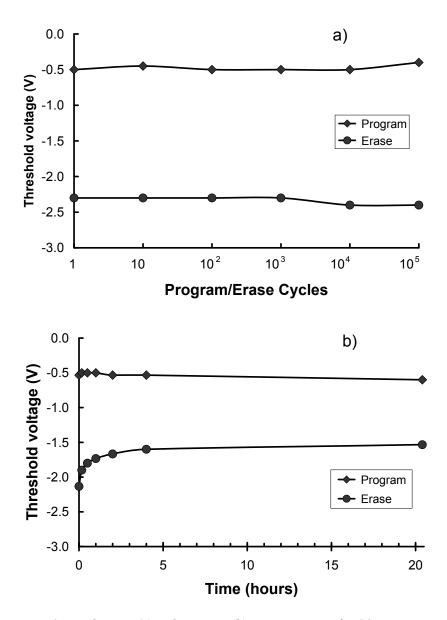

Figure 5.9: Endurance (a) and retention (b) measurements of MOS structures with encapsulated silicon nanocrystals

As charge is stored in the nanocrystals, i.e. between the substrate and the control gate, it dramatically influences the C-V characteristics of the

MOS capacitors. Figure 5.8 shows typical hysteresis curves observed during the quasi-static C-V measurements of the circular (500  $\mu$ m in diameter) MOS capacitors with embedded nanocrystals. The width of the hysteresis corresponds to the threshold voltage shift ( $\Delta V_{\rm T}$ ). Herewith, it can be concluded that the capacitors work as a memory cell.

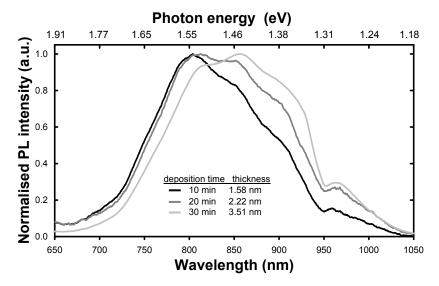

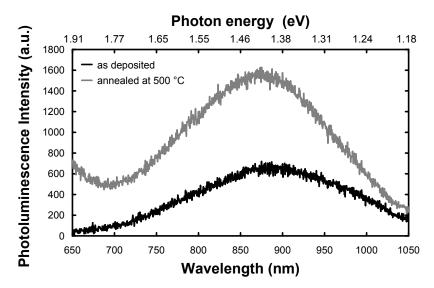

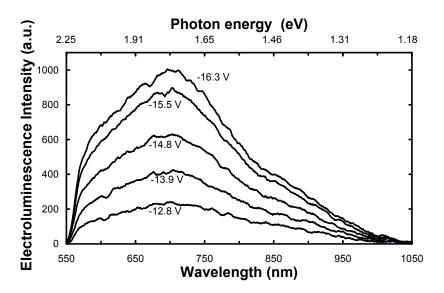

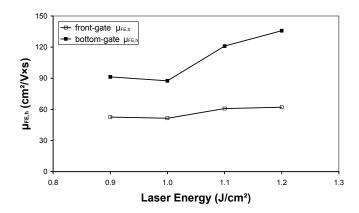

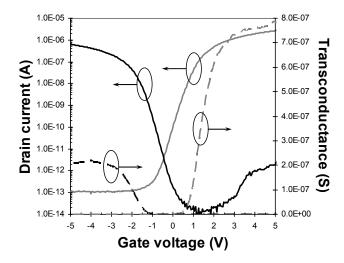

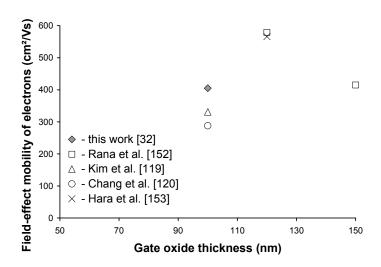

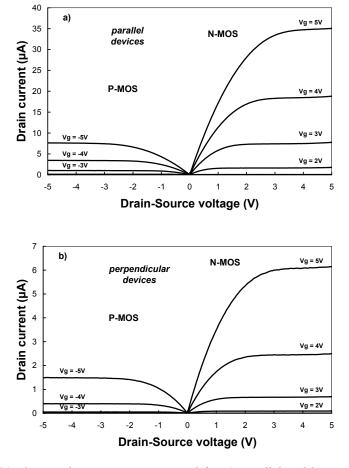

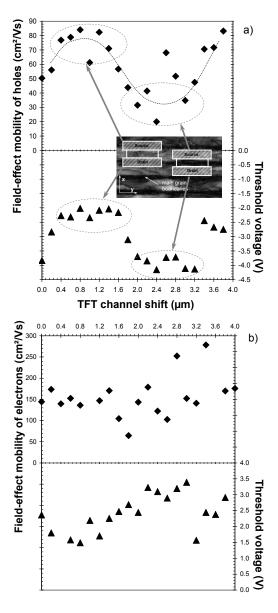

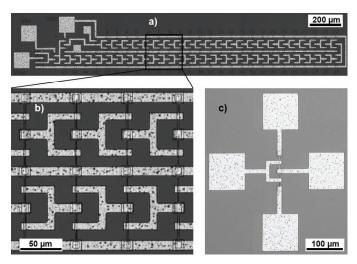

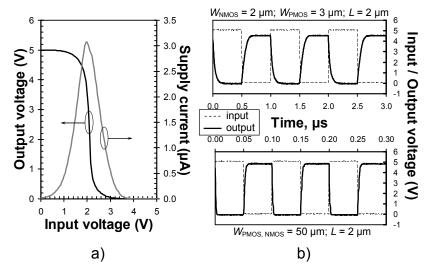

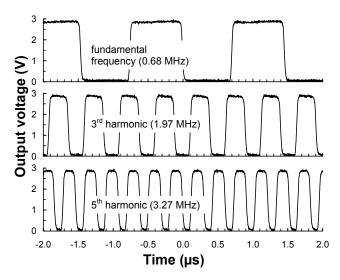

To characterize programming and erasing behaviour of the multilayer structure, the endurance (Figure 5.9a) and retention (Figure 5.9b) of the above mentioned MOS capacitors were tested. The test devices were programmed by biasing the gate at  $V_{\rm G\,prog} = 3.5\,\rm V$  and erased by biasing the gate at  $V_{\rm G\,erase} = -5.5\,\rm V$ . Figure 5.9a shows a good endurance after  $10^5\,\rm program/erase$  cycles, meeting basic flash memory cell requirements.